RCSADC12BRH

FEATURES

- Single 12-Bit Synchronous ADC

- Successive Approximation Register Architecture

- Operating Voltage: 1.2V and 3.3V±10%

- Max clock rate: 10MHz

- Max data rate: 625kSPS

- Low Power Consumption:

- Normal: 7 mW typical max (including pad)

- Power-down: 6 mW max (including pad)

- CMOS digital output

- End-of-Conversion output for bit synchronization

- Start and Reset pins

- On-chip wide input range buffer (1÷2 Vpp)

- Power-down control via PD pin

- Fully-differential and Single-Ended operation

- Wide Temperature Range: -55 to +125°C

- Radiation Hardened process and design:

- Total Dose 300 krad(Si) (Co60)

- SEL LETth > 60 MeV/mg*cm2 (Si) (Xe Ions)

- 4 < SEU LETth < 5 MeV cm2/mg (Si)

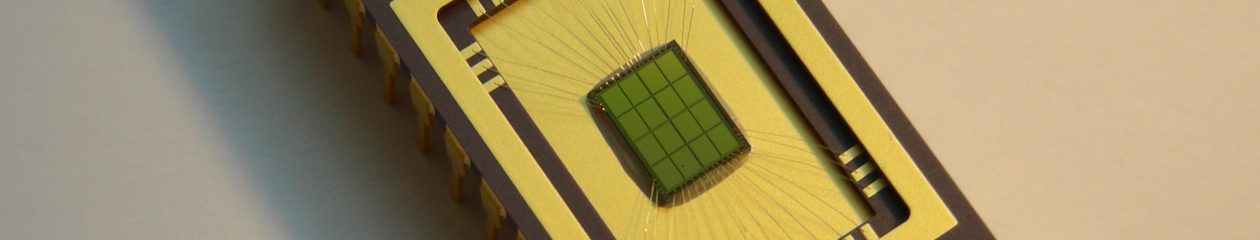

- Packaging options:

- no package (waffle pack die)

- CERQUAD (only for evaluation)

APPLICATIONS

- Space

- Industrial

DESCRIPTION

RCSRDAC12BRH is a low power 12-bit Analog-To-Digital converter that can be used with a typical sample rate up to 200kSPS. A maximum sample rate of 625kSPS is admitted with a small performance degradation. It operates from two supply voltages (1.2V and 3.3V) for the ADC core and I/O with a total power consumption of 7 mW.

The device incorporates an End-of-Conversion output signal allowing output bit synchronization.

A standard CMOS technology has been used to implement RCSRDAC12BRH with a dedicated robust rad-hard by design (RHBD) approach using ELT transistors and enhanced guard rings.

RCSDAC12BRH has been specifically designed for applications with TID requirements in range of 100krad-300krad such as LEO, MEO and GEO.