Synchronous Single Port SRAMs

DESCRIPTION

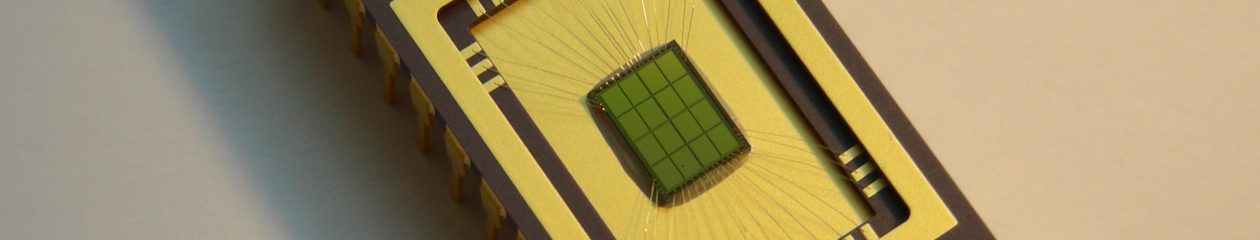

RC7CSSP SRAMs are a low voltage, high performance, synchronous, rad hard 1024 words x 1bit single-port memory device using 6T memory cells. Macros include internal SET (Single Event Transient) filters to avoid soft errors running in the clock tree and uses EGRs (Enhanced Guard Rings) to guarantee protection against SEL (Single Event Latch-up). For TID (Total Ionizing Dose) mitigation in peripheral logic ELTs (Edge-less Transistors) have been used while in 6T memory cells IGRs (Island Guard Rings) have been used to reduce parasitic resistance on word-lines and bit-lines and to protect the memory element against SELs. Thanks to independent decoding schemes macros have only SEUs (Single Event Upsets) and no MBUs (Multiple Bit Upsets).

A standard 0.18µm CMOS 6 metals technology process has been used.

RC7CSSP SRAMs can be used in digital ASICs for space application in almost all orbits (LEO, GEO, HEO) and in terrestrial application in hostile environments (medical radiology, sterilization, nuclear reactors/plants).

RC7CSSP SRAMs are delivered with documentation, liberty description (.lib), verilog (.v), abstract (.lef) and full extracted netlist for making extended spice and verilog simulations.

Single Port SRAMs:

RC7CSSP1K1B (1024 x1 SPSRAM)

RC7CSSP1K8B (1024 x8 SPSRAM)

RC7CSSP1K16B (1024 x16 SPSRAM)

RC7CSSP2K1B (2048 x1 SPSRAM)

RC7CSSP2K8B (2048 x8 SPSRAM)

RC7CSSP2K16B (2048 x16 SPSRAM)

RC7CSSP4K1B (4096 x1 SPSRAM)

RC7CSSP4K8B (4096 x8 SPSRAM)

RC7CSSP4K16B (4096 x16 SPSRAM)

RC7CSSP8K1B (8192 x1 SPSRAM)

RC7CSSP8K8B (8192 x8 SPSRAM)

RC7CSSP8K16B (8192 x16 SPSRAM)

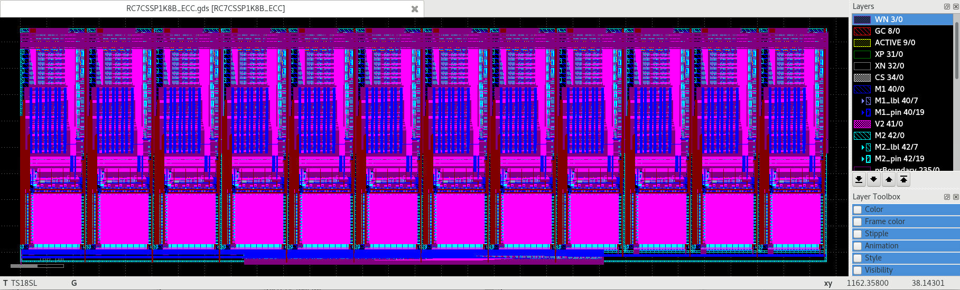

Rad Hard 1024 x8 Synchronous Single Port SRAM with ECC

Rad Hard 1024 x8 Synchronous Single Port SRAM with ECC